Discover how the RISC-V architecture is democratizing hardware.

RISC-V: The Open Source CPU Revolution

For decades, the semiconductor industry was a fortress guarded by a few elite architects. If you wanted to build a computer, you played by Intel’s rules with x86; if you wanted a smartphone, you paid royalties to ARM. But in 2026, those walls have effectively crumbled. We are living through the democratization of hardware, a movement sparked by a simple yet radical idea: an open standard ISA (Instruction Set Architecture) called RISC-V.

What began as an academic project at UC Berkeley has evolved into a global phenomenon. RISC-V is not just a piece of technology; it is a declaration of independence for chip designers, offering a royalty-free, highly customizable alternative to the proprietary giants.

The Core of the Movement: RISC-V Architecture

At its heart, the RISC-V architecture is based on Reduced Instruction Set Computer (RISC) principles. Unlike the "CISC" (Complex Instruction Set Computing) approach of x86, which uses a massive library of instructions to handle tasks, RISC-V utilizes a small, efficient base set of instructions. In early 2026, market data indicates that RISC-V has officially captured 25% of the global processor market, a testament to its technical viability.

However, its true power lies in its modularity. While ARM and x86 are "black boxes"—where you must license the entire architecture even if you only need 10% of it—RISC-V allows designers to start with a tiny core and add only the specific extensions they need. This modularity is the catalyst for a new era of custom chip design, where silicon is tailored specifically for the software it will run, rather than software being forced to fit general-purpose hardware.

Why Tech Giants Are Jumping Ship

The shift toward RISC-V isn't just about saving money on licensing fees; it’s about control. In an era of geopolitical instability and supply chain fragility, tech giants like Google, Nvidia, and Meta are seeking "architectural sovereignty."

- Zero Royalties: By using an open standard ISA, companies can redirect millions of dollars from licensing fees toward internal R&D.

- Unmatched Customization: In the race for AI supremacy, general-purpose chips are no longer enough. RISC-V allows engineers to create "custom instructions" that can accelerate specific AI workloads, such as tensor math or neural network processing, directly at the hardware level.

- Vendor Independence: With RISC-V, a company isn't tied to the roadmap of a single vendor like ARM. If one supplier fails to innovate, the company can take the open specifications to another manufacturer or even design their own in-house core.

RISC-V in Embedded Systems: The First Frontier

While high-performance computing (HPC) and data centers are the ultimate goals, embedded systems have been the primary theater for RISC-V’s early victories. From smart thermostats and automotive sensors to medical wearables, the architecture's low power consumption and small silicon footprint make it a natural fit. Reports show that by 2025, over 20 billion RISC-V cores were already in use globally, predominantly in these segments.

In 2026, the complexity of embedded systems has skyrocketed. These devices now require on-device AI inference and robust cybersecurity. Because RISC-V is open-source, researchers and security firms can scrutinize the ISA for vulnerabilities more transparently than they ever could with proprietary designs. This has led to the development of "hardened" RISC-V cores that are now standard in industrial automation and critical infrastructure.

The Democratization of Hardware

Perhaps the most profound impact of RISC-V is the democratization of hardware. Historically, designing a custom chip required a budget of tens of millions of dollars and a legal team to navigate licensing. Today, a startup in Lagos or a research lab in Mumbai can download the RISC-V specifications and begin building. This shift has enabled a 30% CAGR in the RISC-V market, allowing smaller players to enter the semiconductor space once dominated by a few giants.

This has sparked an explosion of "domain-specific silicon." We are seeing chips designed specifically for:

- Edge AI: Real-time gesture recognition in AR glasses.

- Automotive: Specialized controllers for autonomous driving that meet strict safety standards like ISO 26262.

- Space Exploration: Radiation-hardened processors for satellite constellations.

Industry Adoption: Crossing the Chasm

The phrase "industry adoption" used to be a question mark for RISC-V. Today, it is a statement of fact. In 2026, more than 30% of new IoT designs and a rapidly growing share of automotive silicon are based on RISC-V.

Major milestones include:

- Automotive Alliances: Leading European and Asian carmakers have formed joint ventures to develop RISC-V based platforms, reducing their reliance on proprietary IP.

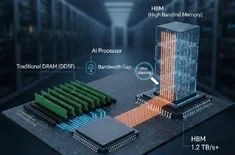

- Data Center Breakthroughs: Hyperscalers have begun deploying RISC-V "sidecar" processors to handle security, storage, and networking tasks, freeing up main CPUs for heavy compute.

- Mobile Integration: While ARM still leads the smartphone market, RISC-V has taken over "background" chips—managing everything from battery life to Wi-Fi connectivity.

Technical Comparison: RISC-V vs. The Incumbents

| Feature | RISC-V | ARM | x86 (Intel/AMD) |

|---|---|---|---|

| Licensing | Open Standard (Free) | Proprietary (Expensive) | Proprietary (Closed) |

| Customizability | Fully Extensible | Limited | Virtually None |

| Ecosystem | Rapidly Growing | Mature | Extremely Mature |

| Philosophy | Modular & Lean | Integrated | Complex |

The Road Ahead: 2026 and Beyond

The RISC-V revolution is not just about a technical specification; it is about a shift in the power dynamics of the world. By providing a common, open language for compute, RISC-V has ensured that innovation is no longer a luxury reserved for the few. As software parity is achieved through projects like RISE, the "software gap" has effectively closed, making RISC-V a Tier-1 architecture alongside its peers.

As we look toward the end of the decade, the focus is shifting from "Can RISC-V do it?" to "How much better can RISC-V do it?" With the maturation of software toolchains and the support of the world's largest tech companies, the open-source CPU revolution is no longer a prediction—it is the new foundation of the digital age.